RHD

# **Dual Headstage Adapter**

20 September 2016; updated 27 May 2021

#### **Features**

- ♦ Allows two RHD headstages to share a single SPI interface cable

- Flexible design allows amplifier boards to be repositioned in different configurations

### **Applications**

- High density RHD-based electrophysiology signal acquisition systems

- Starting point for the development of dual-chip headstages using RHD2000 chips

#### **Description**

All SPI interface cables from Intan Technologies support data streams from two RHD2000 chips. The **dual headstage adapter** allows two RHD headstages (i.e., amplifier boards) to be connected to a single SPI interface cable. This allows for high-density recording modules using only one all-digital cable (e.g., a 128-channel recording headstage using two RHD2164 chips).

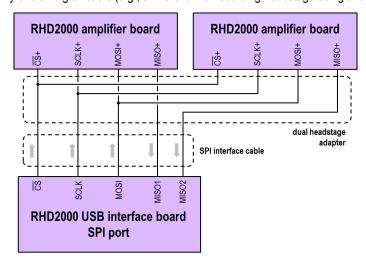

**Figure 1.** Simplified block diagram of a dual headstage adapter connecting two RHD headstages (amplifier boards) to a single SPI interface cable. Power wires are not shown.

**Figure 2.** Two RHD 64-channel amplifier boards (one with an accelerometer) attached to a **cable-style dual headstage adapter** to create a 128-channel module using a single SPI interface cable.

Figure 1 shows a simplified block diagram of a dual headstage adapter connecting two RHD headstages to a single SPI interface cable. The two RHD2000 chips share the chip select (CS), serial clock (SCLK), and MOSI (master out, slave in) signals transmitted from the RHD controller, so both chips receive identical commands over the SPI bus. The dual headstage adapter connects the MISO (master in, slave out) signal from each RHD2000 chip to the two MISO lines (MISO1 and MISO2) present in the SPI interface cable and supported by the RHD recording controller or RHD USB interface board. (See the RHD2000 series datasheet and the Rhythm interface datasheet for more details on this 4-wire SPI communication protocol.)

The **dual headstage adapter** (Part #C3442) is shown in Figure 2. The adapter uses self-aligning 12-pin Omnetics PZN-12 polarized nano connectors at each end. An SPI interface cable should be plugged into the center connector and RHD headstages should be attached to the left and right connectors, as shown in Figure 2.

The RHX open-source interface software seamlessly supports dual-headstage operation. The channels from both amplifier boards on a single SPI port are appended in the graphical user interface (GUI). To see additional channels, simply click on the waveform display and use the cursor keys to scroll down to additional channels. The channels from the amplifier board attached to the MISO1 connector appear first; the channels from MISO2 appear next. Headstages of different types may be combined using the dual headstage adapter.

#### **Optimization for Operation with Long Cables**

If the dual headstage adapter is used with daisy-chained SPI interface cables exceeding 6 feet (1.8 meters) in total length, it may be necessary to modify one of the amplifier boards by removing three small resistors to maintain high fidelity of the digital signals on the cable. This section describes the rationale and procedure for making this modification.

Digital signals in the SPI interface cables are transmitted using low-voltage differential signaling (LVDS) on twisted-pair wires. According to LVDS standards, the common-mode voltage on these wires is held near 1.25V, and the differential voltage between a pair of wires is either +350 mV (to represent logic high or digital "1") or -350 mV (to represent logic low or digital "0"). The characteristic impedance  $Z_0$  of the twisted pairs inside the SPI interface cable is close to  $100~\Omega$ , which means that each pair should be terminated with a  $100~\Omega$  resistor to prevent reflections on the cable during high-frequency signaling. Reflections can lead to corrupted digital data.

(Note: The characteristic impedance of a cable is unrelated to the DC resistance of the actual wires; rather, it is the square root of the ratio of the cable inductance per unit length to the cable capacitance per unit length. Its value is related to how high-frequency signals propagate down the cable.)

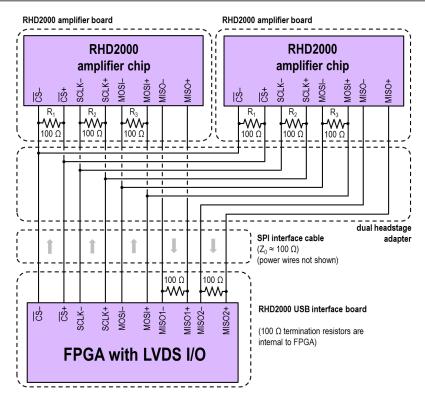

Each RHD headstage has three  $100~\Omega$  termination resistors labeled  $R_1$ ,  $R_2$ , and  $R_3$ , that terminate the LVDS signals for chip select ( $\overline{CS}$ ), serial clock (SCLK), and MOSI (master out, slave in), the SPI signals that send commands to the RHD2000 chips. The termination resistors for the MISO (master in, slave out) signals returning data from the chips are located internally on the Xilinx FPGA that resides on the RHD recording controller or RHD USB interface board. Figure 3 shows a simplified schematic of two RHD headstages connected through a dual headstage adapter and SPI interface cable to a controller.

In this diagram, it can be seen that the  $100~\Omega$  termination resistors  $R_1$ ,  $R_2$ , and  $R_3$  from the two amplifier boards are connected in parallel when a dual headstage adapter is used. This parallel combination of resistors reduces the effective termination resistance to  $50~\Omega$ , which is not optimal for LVDS operation. As a result, reflections will be present on the SPI interface cable, and this can lead to corrupted digital data when long cables are used.

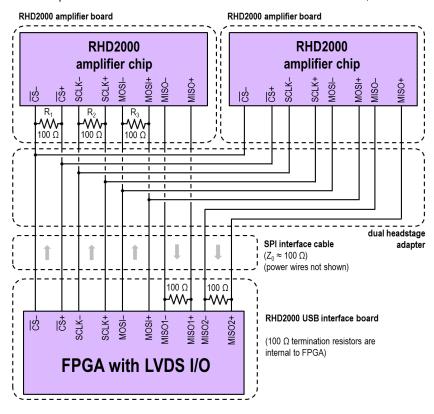

In experiments performed at Intan Technologies, using cables totaling 6 feet (1.8 meters) in length did not result in corrupted data when using two headstages with all termination resistors in place. However, longer total cable lengths (e.g., from daisy-chaining multiple SPI cables) can lead to corrupted data that is clearly visible in the software display. In this case, the data fidelity may be restored by removing the  $R_1$ ,  $R_2$ , and  $R_3$  termination resistors from one (and only one) of the two amplifier boards to bring the total termination resistance back to 100  $\Omega$ , as shown in Figure 4.

It does not matter which amplifier board has its termination resistors removed, but once they are removed this amplifier board may suffer from low data fidelity if it is used by itself (i.e., without the dual headstage adapter) with long cables since its effective termination resistance is now nearly infinite.

The resistors  $R_1$ ,  $R_2$ , and  $R_3$  are small black components with silver-colored ends that are clearly marked on all amplifier board printed circuit boards. (Do not confuse them with  $R_0$ , which is a 0  $\Omega$  resistor that optionally shorts the reference electrode to ground.) They may be removed using a fine-tipped soldering iron, but soldering tweezers (optimized for surface-mount components) sold by Weller or other companies make the job particularly easy. After removing the resistors, make sure that no residual solder is bridging the gap on the circuit board and creating a short circuit.

The termination resistances for the MISO lines are not affected by the dual headstage adapter since there are two independent lines (MISO1 and MISO2) each having its own termination resistor in the FPGA on the USB interface board or recording controller.

**Figure 3.** Simplified schematic of dual headstage adapter with 100  $\Omega$  termination resistors shown. The parallel combination of termination resistors on two amplifier boards results in effective termination resistances of 50  $\Omega$ , which is non-optimal.

**Figure 4.** Simplified schematic of dual headstage adapter with 100  $\Omega$  termination resistors removed from one amplifier board. The effective termination resistance has been restored its optimum value of 100  $\Omega$ .

#### **Related Documentation**

Complete schematics and design files of the dual headstage adapter, along with the following supporting datasheets may be found at www.intantech.com/downloads:

- ♦ RHD SPI Cable / Connector Specification

- ♦ RHD Application Note: Adapting SPI Cables to a Commutator

- ♦ RHD Series Digital Electrophysiology Interface Chip Datasheet

- RHD Evaluation System User Guide

- ♦ RHD Recording System User Guide