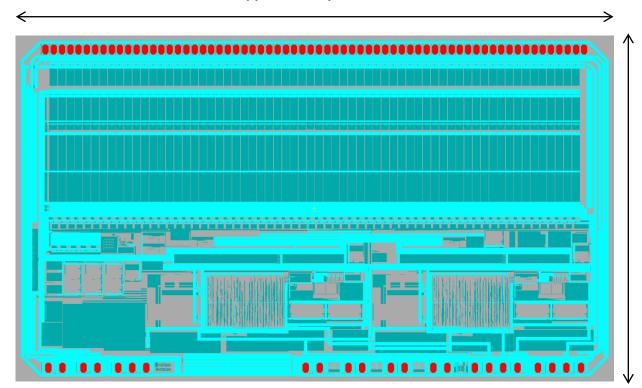

## **Intan Technologies RHD2164 Bare Die**

#### Approximately 7.3 mm

Gray = approximate outline of die (may vary from die to die due to variations in sawing)

Yellow Cross = center of design (may not coincide precisely with center of die due to variations in sawing)

Blue, Green = top metal layers (highly visible)

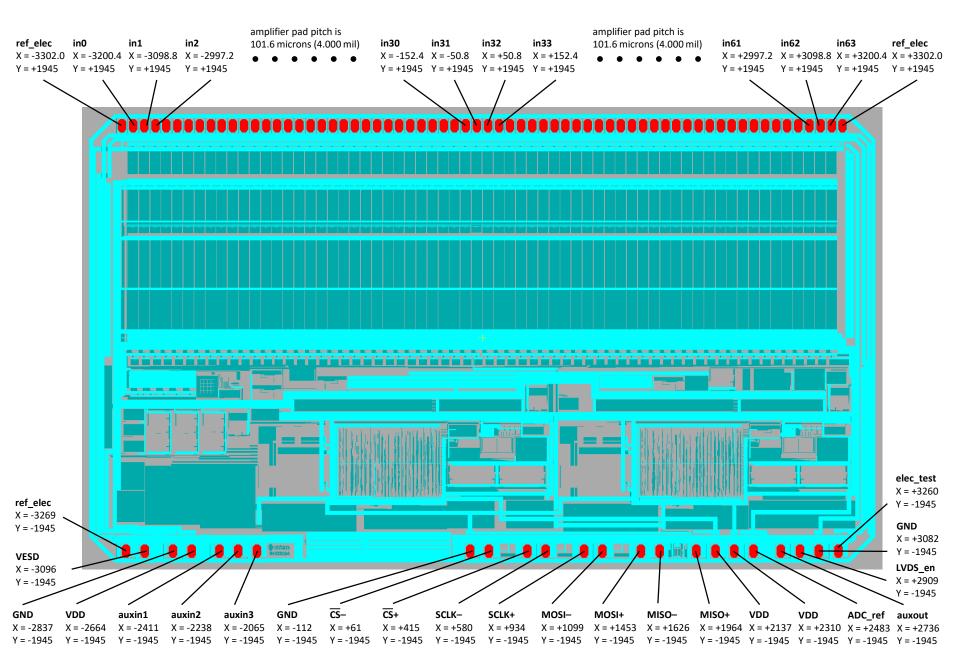

**Red** = glass openings for bond pads

Approximately 4.2 mm

Each die is 0.20 mm (8 mils) thick

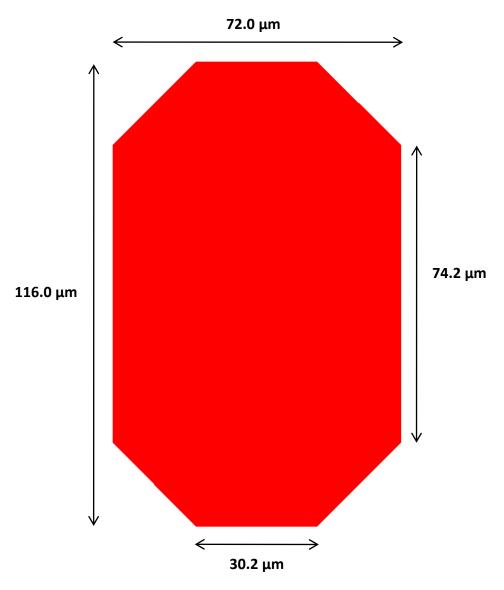

### **Bond Pad Dimensions**

Bond pad metal: AlCu (99.5% aluminum, 0.5% copper)

Minimum bond pad pitch (center to center) on RHD2164: 101.6  $\mu$ m (4.000 mil)

### **Notes on Optional Bond Wires**

Each RHD2164 die has three bondpads for the reference electrode connection (labeled **ref\_elec**). These are located in the upper left, upper right, and lower left corners of the chip. These pads are connected internally on the chip, so only **one** of these pads needs to be bonded. There is no advantage to bonding more than one of these pads. Multiple bond pads are provided only for circuit board layout convenience.

There are three ground pads and three power pads (labeled **GND** and **VDD**). **All six** of these pads **must** be bonded and connected to the appropriate supply voltages for proper operation. An off-chip 100 nF capacitor between ground and VDD should be placed less than 1 cm from the lower edge of the chip. For best operation, this capacitor should have an X5R or X7R dielectric and should be rated for at least 16V. If non-LVDS (standard CMOS) signaling is used, it is recommended that two 100 nF capacitors be used: one near the lower left corner of the chip and one near the lower right corner of the chip.

The **ADC\_ref** pin must be bonded and connected to an off-chip 10 nF capacitor to ground, which should be placed within 1 cm of the lower edge the chip. This capacitor should have an X5R, X7R, COG, or NPO dielectric and should be rated for at least 16V. If multiple RHD2164 chips are used, each chip must have its own 10 nF capacitor. The **ADC\_ref** pins of different chips should not be connected.

The **VESD** pad must be bonded and connected either to ground (recommended) or to VDD. See the "Amplifier Input Protection" section of the RHD2000 series datasheet for more information on this pin.

It is not necessary to bond the auxin1, auxin2, or auxin3 pins if auxiliary analog signals will not be connected to the chip.

It is not necessary to bond the auxout pin of the auxiliary digital output will not be used.

In most applications, the **elec\_test** pad should remain unbonded. This pad is typically used only to provide DC voltages for the purposes of electrode activation or electroplating. See the "Electrode Activation" section of the RHD2000 series datasheet for more details.

The **LVDS\_en** pad of the RHD2164 chip has an internal pull-up resistor that enables LVDS signaling on the SPI bus if this pad is left unbonded. If non-LVDS (standard CMOS) SPI signaling is desired then this pad must be bonded and connected to ground.

If LVDS SPI signaling will be used, than all eight SPI pads ( $\overline{\text{CS}}$ –,  $\overline{\text{CS}}$ +, SCLK–, SCLK+, MOSI–, MOSI–, MISO–, MISO+) must be bonded. If non-LVDS (standard CMOS) SPI signaling will be used, the negative SPI pins ( $\overline{\text{CS}}$ –, SCLK–, MOSI–, MISO–) can remain unbonded.

# **Suggested PCB Footprint for Chip-on-Board Assembly**

dimensions in mils (1 mil = 0.001 inch = 25.4 microns) pitch = 4 mil 16 mil 8 mil x 2 mil pads (66x) electrode pads are centered with respect to large pad 304 mil x 184 mil pad (1x)22 mil → **←** 24 mil 8 mil x 4 mil pads (23x)16 mil pitch = 8 mil pitch = 10 mil pitch = 8 mil

Immersion gold finish (ENIG) or similar planar, bondable finish should be used on PCB.